Phone +45 3967 6438 Fax +45 3966 6438 Website www.rostec.dk E-mail rostec@rostec.dk

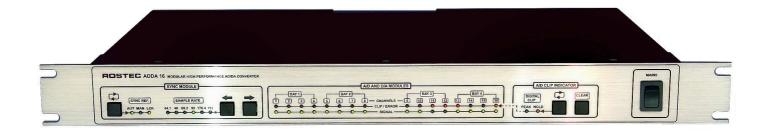

## ADDA16 AD/DA Converter

ADDA16 Modular High Performance AD/DA Converter Revision 3, August 20, 2012

| General description                                |     |

|----------------------------------------------------|-----|

| Contents                                           | . 1 |

| Features                                           | . 2 |

| General description                                | . 2 |

| The AD converter                                   | . 2 |

| The DA converter                                   |     |

| The sync generator                                 | 2   |

| The analog circuits                                | 3   |

| The digital interface                              | 3   |

| Operational description                            |     |

| Selecting sync input mode and sample rate          | 4   |

| Using the clock module as a master clock generator |     |

| Selecting AD peak indicator mode                   |     |

| Channel status indicators                          |     |

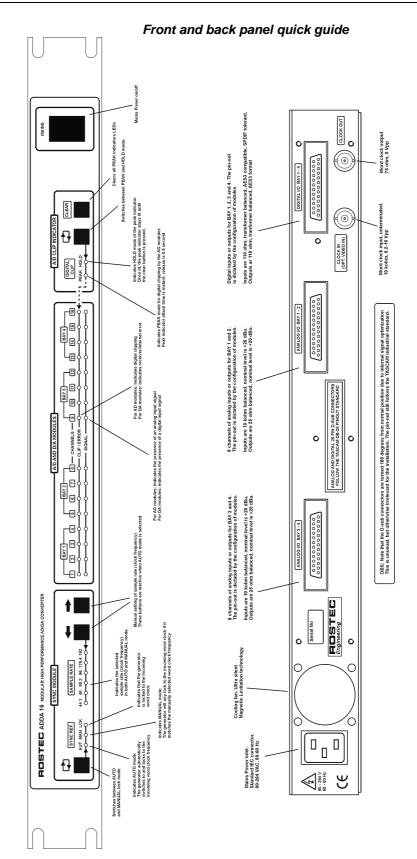

| Front and back panel quick guide                   |     |

| Removing and installing modules                    |     |

| Back panel connections                             |     |

| Example: A TASCAM compatible configuration         |     |

| Sync connections                                   | 11  |

|                                                    |     |

| Mechanical and electrical specifications           | .13 |

| Technical section                                  |     |

| Simplified functional schematic                    |     |

| Overload and clipping                              |     |

| Distortion characteristics                         |     |

| Distortion in depth analysis                       |     |

| Crosstalk                                          |     |

| Synchronization and sync clean-up                  | 22  |

#### **Features**

- 16 channels of AD or DA in 1U box.

- Modular design, several combinations of AD and DA are allowed.

- 24 bit, 192 kHz latest generation converters.

- Dynamic range 120 dB for AD converters and 118 dB for DA converters.

- Low latency.

- Transformer balanced AES in- and outputs.

- Easy interfacing via standard D-sub connectors.

- Includes Grade 2 word clock generator.

- Auto detection of incoming sampling frequency.

- Exceptional high immunity to jitter and digital noise from computer work stations.

- Word clock Input has a "sweet spot" detector, providing auto-slicing and signal clean-up.

- Clock input accept from 0.2 Volts to 10 Volts.

- Balanced analog in- and output buffers.

- Combination of JFET and BJT technology for exquisite sonic performance.

- Analog and digital balanced architecture.

- International power supply, 90-264 VAC.

- Ultra quiet magnetic levitation cooling fan.

- Digital Inputs and outputs are ESD protected to 23 kV, IEC 61000-4-2 and 15 A surge, IEC 61000-4-5.

- 19" sturdy steel metal casing.

- Affordable price.

#### General description

The ADDA16 is a modular low noise low distortion and high performance 24 bit/192 kHz AD or DA converter designed to operate in any film, broadcast, video or audio studio environment.

Its highly efficient synchronization scheme is particular adapted to the modern dynamic studio workflow, and at the same time guards itself against many of the usual installation pitfalls.

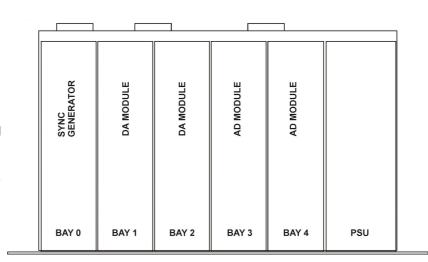

The 1U box contains 1 power supply, 1 slot for the sync generator and 4 slots for the converter modules. Each converter module consists of either 4 channels AD or 4 channels DA. The generator module must always be installed for the converters to function. The converter modules can be installed as needed. A mix of AD and DA modules is allowed.

The converters are all of the latest generation of top performers, based on the newest oversampling multi-bit delta-sigma technology.

### The AD converter

The AD converter chip operates in a very low jitter environment, created by the sync generator, which enables the delta-sigma process to convert with optimum precision.

Normally it is assumed that jitter is not really important in a digital to digital interface, but although this is to some extent true, low jitter is extremely important for the conversion process from analog to digital.

Great effort has been put into creating a low jitter clock system internally. It may not be reflected in the specifications, but it certainly is reflected in the sonic quality!

#### The DA converter

The DA converter is in vulnerable position, as it has to receive its data from outside the box, thus it is victim to any malformed or jittery stream of data from noisy computer workstations.

To overcome this vulnerability, the incoming data stream is fed into a FIFO (First In First Out) buffer memory, and the data is clocked out again by the stable clock from the sync generator.

This scheme is very efficient to solve the issue. As long as the receiver is able to recognize the ones and zeros in the incoming data stream correctly as coherent data, it is fed to the DA chip with low jitter via the FIFO memory buffer, thus creating optimum condition for the conversion from digital to analog.

Again, it may not be reflected much in the specification, but is certainly is reflected in sound quality.

The DA has yet another advantage. If, for some reason, the incoming sync is lost (bad house clock, defect cables), the FIFO immediately switches to sample rate conversion, thus avoiding clicks or pauses in the sound. As soon as the faulty situation is corrected, the FIFO softly switches back to normal memory mode. The only penalty during the sample rate conversion phase is a small increase in latency (less than 1 msec). The sample rate conversion itself has a distortion less than 140 dB.

#### The sync generator

The sync generator is in a class of its own. It is able to automatically detect the incoming word clock frequency and lock on to it without a hitch. It softly glides from the internal crystal reference to external clock without any gaps or interruptions. It achieves lock in typically less than 0.3 seconds, and if the incoming sync is lost, it holds the last good frequency for a while via an internal flywheel before it softly glides over to the internal crystal reference.

Shorter gaps in the incoming sync are efficiently absorbed that way, and the soft gliding back and forth is

sufficiently well damped in order for the delta sigma converter to absorb this without any degradation of sound.

But not all digital equipment work equally elegant when the word clock frequency is changed, so when a new sampling frequency is selected (change of house clock, DAW clock) the ADDA16 immediately detects this and mutes its inputs and outputs instantly.

It organizes itself in a fraction of a second, but it keeps the input and output signals muted for 3 second, after which it opens up again with a soft un-mute. This is meant as a grace period for other equipment to have time to settle.

Everyone that has experienced the ear tearing sound of non-synced digital transfer will appreciate this little detail.

Further, the generator has an extensive ability to clean op a malformed and distorted house clock.

The input uses a high-speed comparator with hysteresis and a "sweet spot" detector, which performs an accurate auto-slicing of the input.

This means that the circuit automatically chooses the most useful part of the input signal, thus being able to clean-up and reconstruct a ringing and noisy input clock into a perfectly shaped output clock.

An input clock with high level of jitter gets the treatment too. The PLL uses a multi pole analog filter network and a digital decimation filter to make it largely immune to jitter.

Put in another way, when the timing of the leading edge of the incoming clock varies (this is what jitter is!) the crystal oscillator won't follow these fluctuations, but chooses the average position of the leading edge of the incoming clock as the reference point. The result is an output clock with typically less than 100 psec RMS jitter. The above is one of the main reasons for the exceptional sonic quality of the ADDA16 converter.

### The analog circuits

The analog circuits use high speed, low noise and low distortion operational amplifiers, chosen, not only for their specifications, but for their sonic qualities as well. The particular chosen combination of JFET technology and Bipolar Junction Technology yields an amazingly open and natural sound that baffles even the most seasoned connoisseurs.

The analog anti-aliasing filters are designed to be minimum phase and linear group delay, using high quality polypropylene capacitor throughout.

Note: Only through-hole capacitors are used. It is well known that SMD polypropylene caps do not always survive the soldering process unscarred, and they are often prone to producing distortion of a nasty kind.

The true balanced architecture of the analog section cancels out a lot of artifact that a digitally busy environment otherwise would induce into the audio path. Another benefit of the balanced signal routing is an increased separation between channels. The ADDA16 has very low channel crosstalk, in spite of the high number of channels in a confined space.

### The digital interface

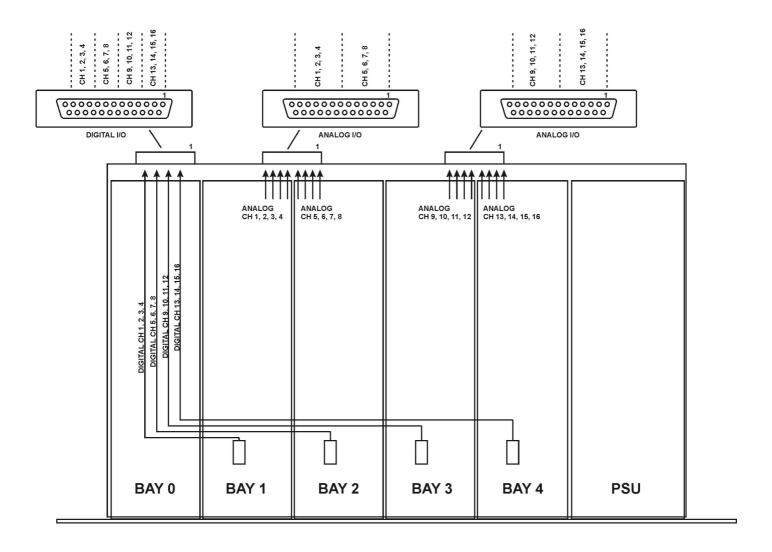

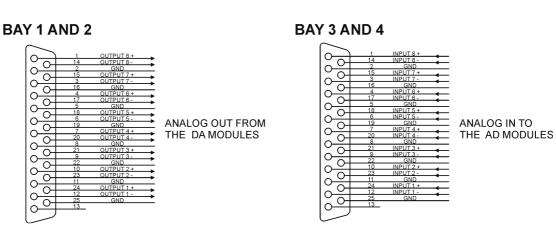

The ADDA16 interfaces to its environment via standard 25 pin D-sub connectors on the back panel. It follows the TACAM DB-25 industrial pin-out standard.

The digital input and output formats are 110 ohm transformer balanced AES3. The input is SPDIF tolerant. Observe that the interface pin-out depends on the configuration of the modules in the box.

For example, if the box is equipped with (seen from the left) 1 word clock generator, 2 DA modules and 2 AD modules, the digital interface is directly pluggable into the HDSPe interface card from RME, or directly pluggable into the digital module of the old Digidesign 192 I/O unit, upgrading the converters to the latest technology.

Also, the analog interface is the same as the 192 I/O unit, so connectors from the existing installation can be plugged directly into the ADDA16. (See back panel connections)

But why the AES interface format?

The AES format is widely used in broadcast, video and audio recording studios, and it is utterly stable and versatile. It leaves room for a flexible infrastructure, where digital equipment can be connected in a myriad of ways and combinations.

There is an excess of interface formats available on the market. The proprietary formats used by various manufacturers are closed systems with a bulk interface for a particular converter type, where the user has little or none access to the digital inputs and outputs. This leaves little room for flexibility, and the user is kind of stuck with the manufacturer.

But there is light on the horizon. USB 3 and Thunderbolt are both very promising solutions. They are flexible, plug and play interfaces with high data carrying capacity, and they are becoming more and more available on quality computer motherboards. The main advantage is that the user is no longer burdened with the task of installing interface card in the DAW, and the monopoly strategy of manufacturers is torn to pieces.

However, the technology is not yet fully matured, but when the time is right, these interfaces will be available on the ADDA16.

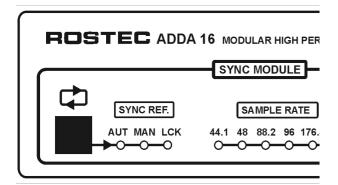

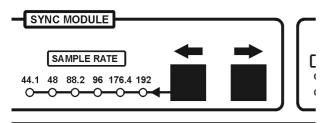

### Selecting sync input mode and sample rate

Pressing the button toggles back and forth between AUTO and MANUAL mode of the input detector.

In AUTO mode, the generator automatically selects the sample rate (output clock) to match the incoming clock frequency. It immediately locks to the signal, and when phase lock between input and output has been achieved, the lock LED lights up. The selected sample rate is indicated by the sample rate LEDs.

In MANUAL mode, the sample rate is selected by pressing the arrow buttons. The buttons switches the sample rate in a ring (i.e. 192 up selects 44.1 and 44.1 down selects 192). The selected sample rate is indicated by the sample rate LEDs.

If the selected sample rate (output clock) matches the incoming clock frequency, the generator will immediately achieve lock, and the lock LED lights up.

16 MODULAR HIGH PERFORMANCE AD/DA CONVERTER

If an input clock is present, the generator will always try to lock to it, no matter if MANUAL or AUTO mode is selected. Note that the incoming clock must be at one of the standard frequencies, and it must have an accuracy that is better than 50 ppm (AES Grade 2 capture range). Observe that clock varispeed is not supported!

#### Using the clock module as a master clock generator

The clock generator module is an excellent, accurate and low jitter master clock generator. Using it as a master is straight forward, just observe these steps:

- 1. There must be absolutely no clock signal present at the clock input connector.

- 2. The input sync mode must be set to MANUAL.

- 3. The sample rate is selected by the arrow buttons. The output clock follows the sample rate.

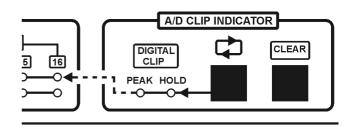

#### Selecting AD peak indicator mode

The clip indicator for the AD module has two modes. The pushbutton switches between them.

When PEAK mode is selected, the clip LED lights up instantly (20 usec) when digital clipping occurs on the corresponding channel. The LEDs stays lit for approx. 0.5 sec after clipping has ceased, giving the eye time to catch the indication.

When HOLD mode is selected, the clip LED stays lit once a clipping has occurred on the corresponding channel. This is useful for checking if any clipping has occurred during a recording session.

When CLEAR is pressed, all clip LEDs are cleared. Switching from HOLD mode to PEAK mode also clears all clip LEDs

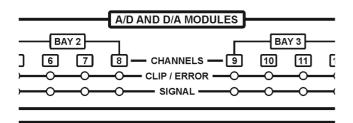

#### Channel status indicators

The channel status LEDs have specific functions that differ for the AD and the DA modules.

For the AD module, the CLIP/ERROR LEDs are digital clipping indicators as describe above.

For the DA module the CLIP/ERROR LEDs light up if an internal error or a digital receiver error occurs. The user will probably never see this indication.

For the AD, the SIGNAL LEDs light up if an analog signal is present at the input of the module on the corresponding channel.

The threshold for the indication is approx -40 dBFS

For the DA, the SIGNAL LEDs light up if a digital signal is present at the input of the module on the corresponding channel.

The threshold for this indication is the LSB of the data stream, which in practice is -144 dBFS.

The channel status LEDs provide identification of the installed modules by giving off a short flash when the unit is powered up, or when the sample rate is changed. A green flash (signal LED) indicates a DA converter module; a red flash (clip/error LED) indicates an AD converter module.

### Removing and installing modules

Installing and removing modules is easy. Just follow these steps.

- 1. Remove the top.

- 2. Disconnect the 4 ribbon cables located near the front end of the AD and DA modules

3. Pull the module upwards at the back end, disconnecting it from the back panel connector using a screwdriver or pliers on the metal ring terminal.

4. Pull the module towards the back of the box, disconnecting it from the front panel connector

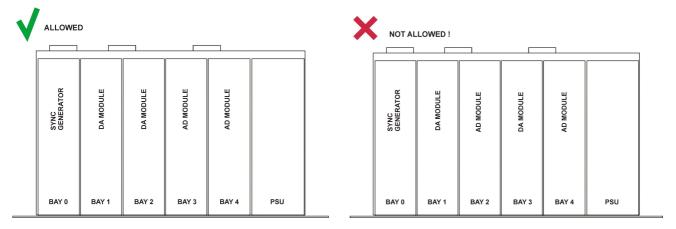

When installing modules, simply perform the above in the reverse order. Almost all combinations of modules are allowed.

However, there are two rules which always must be followed.

- 1. The clock generator must always be installed in BAY 0. It does not matter whether it is a word clock sync, a video sync or a GPS sync. It must always reside in BAY 0.

- 2. If more than one AD converter module is installed, they must reside side by side. Installing a DA module between the AD converter modules is not allowed.

Allowed: The AD modules reside side by side.

Not allowed: A DA module is placed between two AD modules.

### Back panel connections

### Example: A TASCAM compatible configuration

BAY 0: Sync generator BAY 1: DA module BAY 2: DA module BAY 3: AD module BAY 4: AD module

This constitutes 8 input channels and 8 output channels.

The resulting pin-out is shown below. The configuration is compatible with the HDSPe interface card from RME and the old Digidesign 192 I/O.

#### TASCAM STANDARD **DIGITAL I/O COMPATIBLE INTERFACE** OUTPUT 7/8 + -OUTPUT 7/8 - -OUTPUT 7/8 + OUTPUT 7/8 -€ND -0 $\overline{\circ}$ -0 OUTPUT 5/6 + OUTPUT 5/6 -OUTPUT 5/6 + OUTPUT 5/6 -99 GND GND 0 -0 OUTPUT 3/4 + -OUTPUT 3/4 - -OUTPUT 3/4 + OUTPUT 3/4 -GND -0 -0 GND -0 OUTPUT 1/2 + OUTPUT 1/2 -OUTPUT 1/2 + OUTPUT 1/2 -GND Q GND -0 <del>-</del>0 INPUT 7/8 + INPUT 7/8 -INPUT 7/8 + INPUT 7/8 -GND <del>-</del>ō GND -0 INPUT 5/6 + INPUT 5/6 -INPUT 5/6 + INPUT 5/6 --0 -0 GND GND 1919 INPUT 3/4 + INPUT 3/4 -GND GND NPUT 1/2 + NPUT 1/2 -Ō GND Ō

#### Sync connections

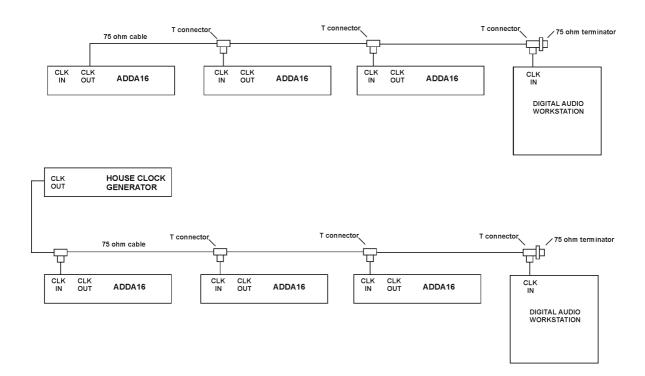

Below is shown the well known "Daisy Chain" connection of the word sync. The upper drawing shows the ADDA16 used as a master clock generator, with the other units slaved to its output word sync. The lower drawing shows all units slaved to a house sync generator.

The daisy chain configuration is based on transmission line theory, which predicts that a perfect transfer of clocks can be achieved when the cable impedance and input and output impedances are the same, in this case 75 ohm.

However, things are not so perfectly ideal when the transmission line is tapped several places between output and input terminations. Especially the last unit in the chain will see a rather distorted clock.

The setup works fine in practice with maybe 4-6 units as long as the cable lengths are kept short. The rule is that units performing AD or AD conversion should be placed first in the chain. Pure digital units, like for example a DAW, is less sensitive to distorted and jittery clocks.

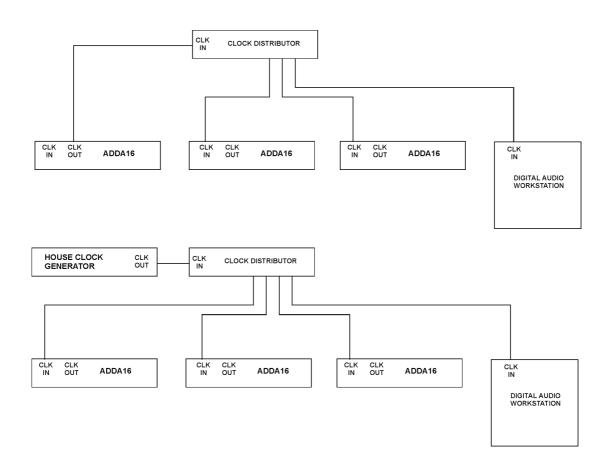

A more correct method is a parallel distribution of clocks, as illustrated below. A clock distributor (distribution amplifier) is used to send individually buffered clocks to the units. The scheme will prevent the units from affecting each others clocks. Termination of the individual clock lines is usually not necessary when the cable lengths are kept short, and quality cables are used. There should be no problems with cable lengths less than 2 meters. Longer cable lengths than that might require terminators at the clock input positions.

#### Mechanical and electrical specifications:

Dimensions : Width 19 inch, height 1U (44 mm), depth 260 mm

Weight : 5.0 kg

**Power** : 90 - 264 VAC, 50-60 Hz, 15 Watts

### **AD converter specs:**

THD+N: -110 dB @ +20 dBu (0.00032%) unweighted

THD: -120 dB @ +20 dBu (0.0001%) unweighted (see detailed measurements section)

Noise floor: -120 dBu, A weighted, ref. full scale

Dynamic Range: 120 dB A weighted

Resolution 24 bits

Sampling frequency: 44.1 k, 48 k, 88.2 k, 98 k, 176.4 k, 192 k

#### **DA converter specs:**

THD+N: -108 dB @ +20 dBu (0.00039%) unweighted

THD: -112 dB @ +20 dBu (0.00025%) unweighted (see detailed measurements section)

Noise floor: -118 dBu, A weighted, ref. full scale

Dynamic Range: 118 dB A weighted

Resolution 24 bits

Sampling frequency: 44.1 k, 48 k, 88.2 k, 98 k, 176.4 k, 192 k

#### **Word Clock Generator specs:**

Accuracy, internal crystal: 1 ppm at 25 degC, factory adjusted Temperature stability: +/-2 ppm from 0 degC to +70 degC

Ageing 2 ppm pr. year

Word clock frequencies: 44.1 k, 48 k, 88.2 k, 98 k, 176.4 k, 192 k

Internal crystal oscillator jitter: 2 ps RMS Word clock output jitter: 100 ps RMS PLL capture range: +/-100 ppm Lock time approx: 0.2 - 0.4 sec

#### **Analog interface**

Analog inputs: 25 pin D-SUB, balanced, 10 kohm, nominal +20 dBu, max +32 dBu

Analog outputs: 25 pin D-SUB, balanced, 25 ohms, nominal +20 dBu

#### **Digital interface:**

ESD protected to 23 kV, IEC 61000-4-2 and 15 A surge, IEC 61000-4-5

Word clock input: BNC, unbalanced, unterminated (10 kohm), sensitivity 0.2 Vpp, max 10 Vpp

Word clock output: BNC, unbalanced, 75 ohm, 5 Vpp

Digital data inputs: 25 pin D-SUB, 110 ohm, transformer balanced, AES3 and SPDIF compatible

Digital data outputs: 25 pin D-SUB, 110 ohm, transformer balanced, AES3 format

### **Technical section**

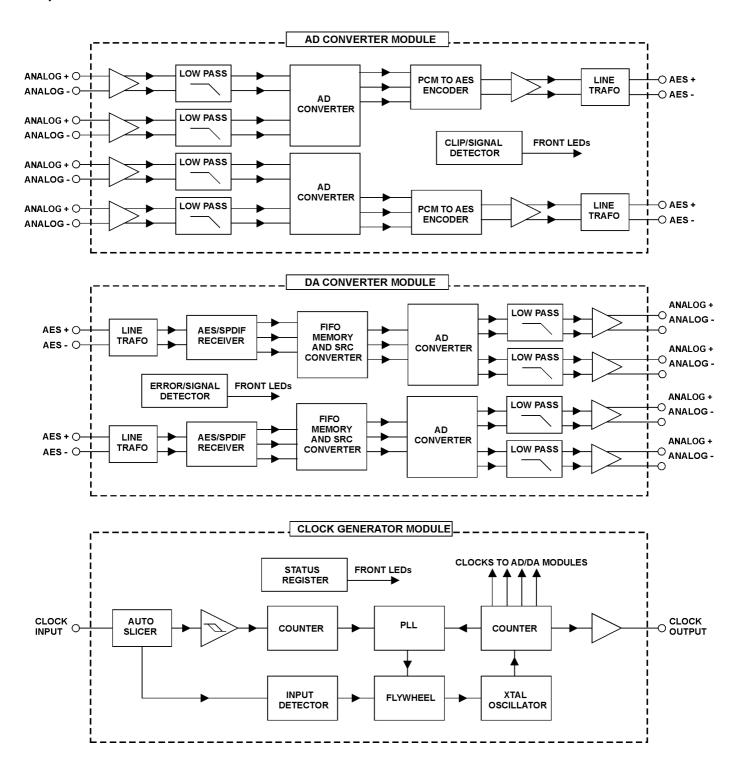

### Simplified Functional Schematic

#### Overload and clipping

Digital clipping has always had a bad name, and with good reason. Most AD converters sound like a total system crash when they are forced into clipping. Various manufacturers have employed elaborate solutions to compensate for this, like input compressors and "soft limiters" etc. This is in reality just swapping one bad thing for another.

The ADDA16 uses a different approach. It is designed to accept input overload as a normal condition, and as a result the clipping characteristics is just like any other high quality analog circuit.

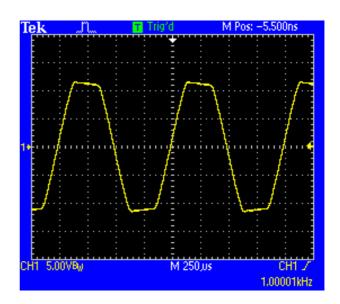

To document this, a sine tone was sent to the AD converter, sent on to the DAW and sent back from the DAW to the DA. The signal was measured at the output of the DA with a digital oscilloscope. Below are some scope snapshots of the clipping characteristics.

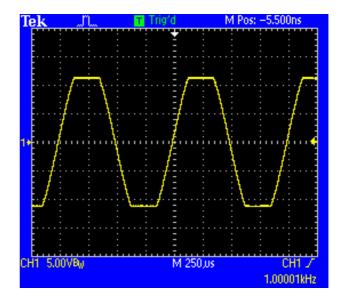

+23 dB input level (+3 dB overload) Sampling frequency: 192 kHz

Frequency: 1 kHz

Measurement bandwidth: 200 MHz.

The output shows moderate clipping. Notice how regular the sine is cut. No overshoot and no recovery delay. This kind of clipping is barely audible

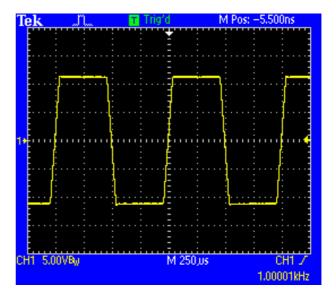

+32 dB input level (+/- 45 V, equals 90 V

peak to peak)

Sampling frequency: 192 kHz

Frequency: 1 kHz

Measurement bandwidth: 200 MHz.

The output shows severe clipping. The input level is far above the output capability of a standard professional console. Again, no overshoot and no recovery delay. And more important, no phase reversal or chopping-up of the signal!

This kind of clipping is clearly audible, but it actually sounds great on drums and bass.

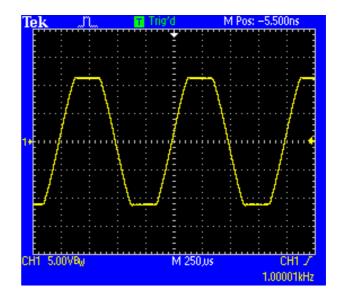

+23 dB input level (+3 dB overload) Sampling frequency: 96 kHz

Frequency: 1 kHz

Measurement bandwidth: 200 MHz.

The output shows clipping that is very close to the clipping characteristics at 192 kHz sampling frequency. Very regular cutting, no overshoot and no recovery delay. The clipping is barely audible

+23 dB input level (+3 dB overload) Sampling frequency: 48 kHz Frequency: 1 kHz

Measurement bandwidth: 200 MHz.

At 48 kHz sampling frequency, the clipping shows a less regular cut. At first glance it looks like lo-cut filtering, but it is actually due to a small ringing from the 100 dB digital anti-aliasing filter in the converter chip. There is absolutely nothing unusual in this. This is how digital filters work.

The clipping is still only barely audible.

#### Distortion characteristics

There has always been focus on distortion, when it comes to judging audio equipment. It can be argued, that any distortion product (2nd, 3rd harmonic etc) below 60 dB is inaudible, simply because the distortion tones are a consequence of the incoming tone, and thus are always masked by it. In some sense this is true, but distortion is more than just sound, it is also an indicator that shows whether there is something wrong with the circuit or not.

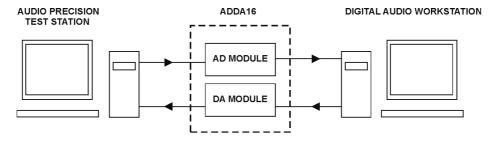

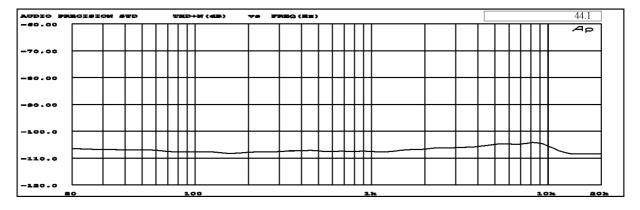

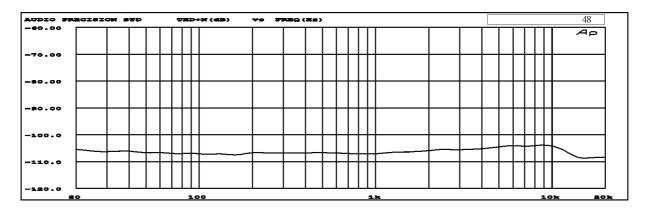

In order to judge the distortion of the ADDA16, the test setup shown below was used. The analog signal from the AP audio analyzer was sent to the AD converter module of the ADDA16. The digital output of the AD was sent to a standard computer work station, and the digital signal from the workstation was returned through the DA converter module back to the AP audio analyzer. That way, all elements of a normal studio audio recording is simulated, right from the microphone input to the sound technician's ears. All noise and distortion from both AD and DA is present, and all the noise and digital jitter from a standard works station is included too. Basically all the dirt that would degrade a recording session is there.

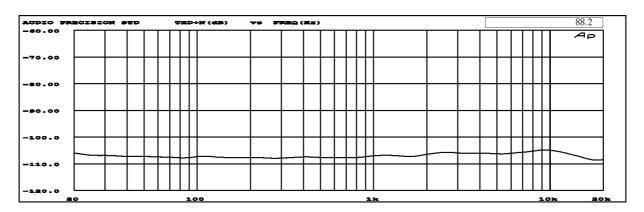

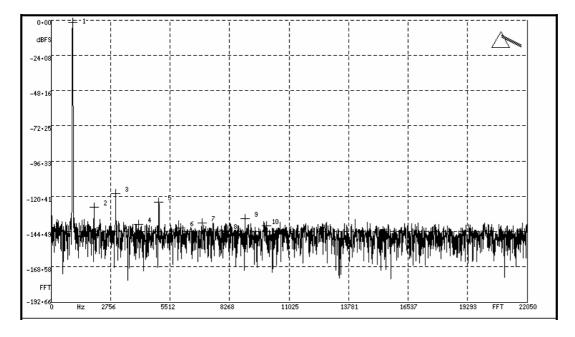

20 Hz - 20 kHz @ -0.2 dBFS, sampling frequency 44.1 kHz

20 Hz - 20 kHz @ -0.2 dBFS, sampling frequency 48 kHz

20 Hz - 20 kHz @ -0.2 dBFS, sampling frequency 88.2 kHz

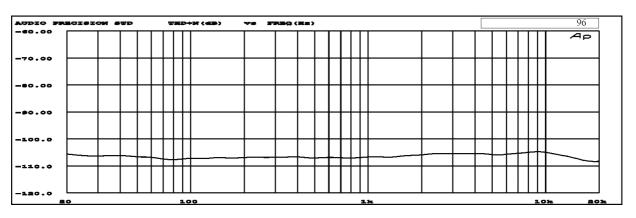

20 Hz - 20 kHz @ -0.2 dBFS, sampling frequency 96 kHz

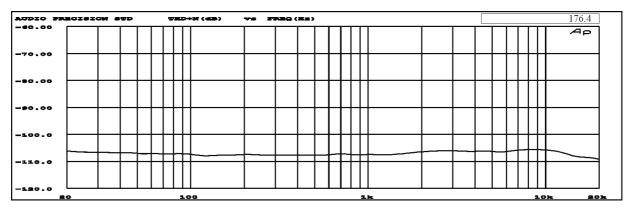

20 Hz - 20 kHz @ -0.2 dBFS, sampling frequency 176.4 kHz

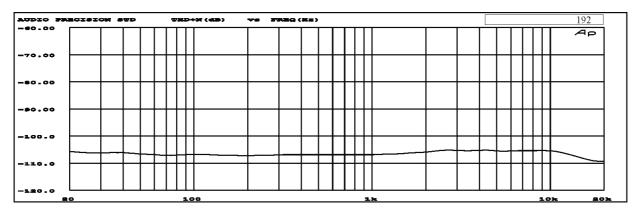

20 Hz - 20 kHz @ -0.2 dBFS, sampling frequency 192 kHz

The distortion lies comfortably in the -105 to -110 dB range for all sampling frequencies. The difference is negligible, showing that sample rate and anti-aliasing filter coefficients are well balanced.

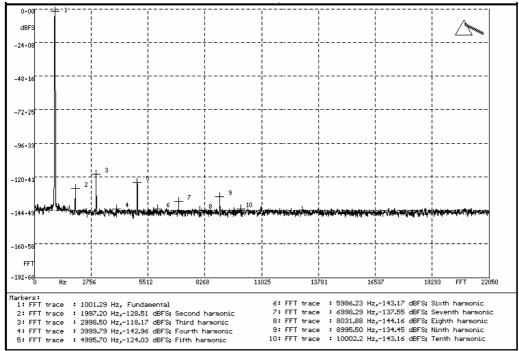

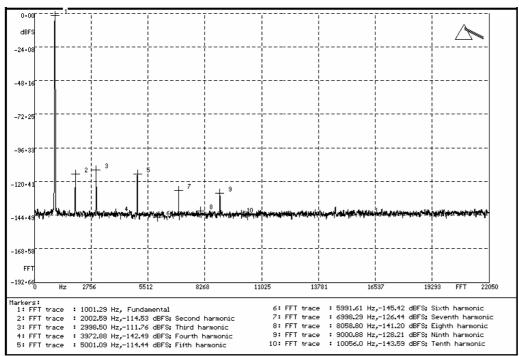

### Distortion in depth analysis

A more detailed picture of the distortion characteristics can be seen using FFT analysis, allowing the magnitude of the individual distortion components to be quantified. In this FFT analysis only the distortion analysis at 44.1 kHz sample rate is included (this is the worst case). Distortion characteristic at the other sample rates are slightly better, approx. 0.5 - 1 dB.

Below is a FFT analysis of the AD converter alone. Notice that the majority of the higher harmonics are buried in the noise floor at -144 dB.

Running 16 FFT passes averages the noise (noise is statistic phenomenon) and makes the picture a lot clearer.

The reading sums up to a THD of -120.08 dBFS

The same test performed routing the signal though both the AD and the DA, shows much the same characteristics:

The reading sums up to a THD of -112.84 dBFS

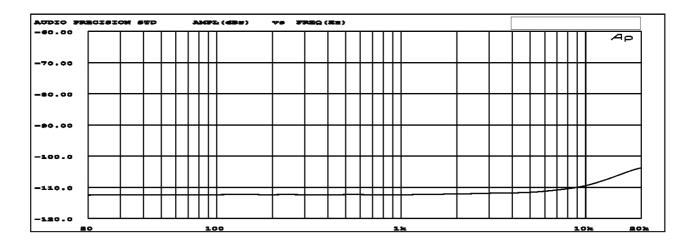

#### Crosstalk

Below is the crosstalk measured between adjacent channels (worst case). A sine sweep from 20 - 20 kHz at full amplitude was sent to one channel, and the output level was measured at the adjacent channel. The channel was terminated by 75 ohm at the input in order to eliminate cable transferred crosstalk.

The true balanced nature of the ADDA16 really pays off. The crosstalk is below -110 dB in the main part of the spectrum. Only above 10 kHz is a slight increase seen, reaching approx. -105 dB at 20 kHz

Note: This is a linear and unweighted measurement. Using A-weighting would give a much better picture, but that would be cheating!

#### Synchronization and sync clean-up

One of the main reasons for the excellent sonic characteristics of the ADDA16 is the ultra low jitter clocks generated by the clock generator module. Besides having a high quality clock output, the module also supplies all the necessary clocks internally to run the DA and AD converters. The excellent jitter characteristic is not really reflected in the electrical specifications, but it is certainly reflected in the perceived sound quality.

In order to safeguard this sound quality in the real world, it is necessary for the module to have a comprehensive jitter and noise rejecting ability.

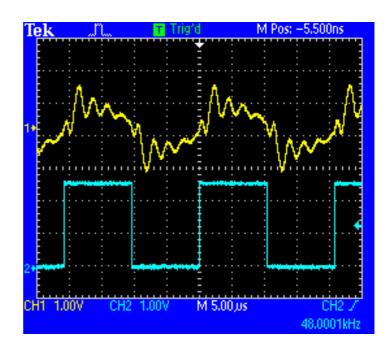

The ADDA16's clock generator module certainly has that. It is able to take in a smashed up word clock and regenerate it into a pure high quality clock. The scope snapshot below shows this ability. The upper trace is an incoming clock that is noisy and severely distorted. The lower trace shows the perfectly regenerated output clock.

The input uses a high-speed comparator with hysteresis and a "sweet spot" detector, which performs a highly accurate auto-slicing of the input.

This means that the circuit automatically chooses the most useful part of the input signal, thus being able to clean-up and reconstruct a ringing and noisy input clock into a perfectly shaped output clock. This kind of distortion is usually due to low quality cable, wrong signal routing or wrong termination. Such a distortion is normally "steady state" which means that a repetitive and useable part of the signal exists. And if it exists, the sweet spot detector will find it!

Another threat to clock integrity is jitter. A small amount of jitter is to some extent irrelevant for a pure digital receiver interface. As long as the digital interface can recognize the ones and zeroes in the data, a coherent data stream can be received and processed.

It is a totally different matter when it comes to AD or DA conversion. A delta sigma converter needs to know the exact position of its clocks all the time in order for it to make a correct sampling of the analog signal. An incorrect sampling, due to clock jitter, produces artifact that for the most part is removed by the digital filters, and the increase in distortion is often measured as no more than a couple of dB. But the impact on the subjectively perceived sound quality is huge. The effect is a flat sound with loss of depth perspective and loss of perception of the environment.

The ADDA16's clock module has a firm and merciless attitude towards incoming jitter: Eliminate it!

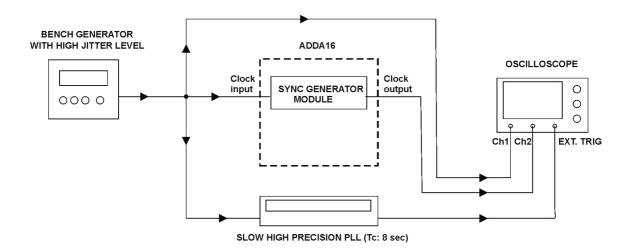

In order to measure the jitter performance of the clock module, a highly stringent and revealing method was used. The block schematic shows the test setup. A standard DDS based test bench generator was used as the source. The jitter spectrum was measured to go from approx 60 Hz to well above 100 kHz. The magnitude of the jitter was 15-20 nsec PP. The signal was sent to a slow moving, high accuracy PLL based on an oven controlled Stratum 2 coldweld VCXO, and it was also sent to the input of the ADDA16 clock module. The output of the slow PLL was used as an external trigger to the scope on channel 3, providing a solid and steady reference for the measurement.

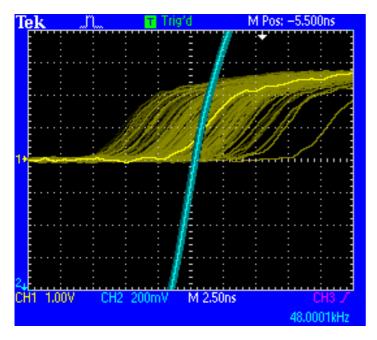

The PLL took ages to lock to the generator, but once done, the outputs of the generator and the clock module were measured by the Tektronix oscilloscope with the output of the PLL as the reference. All signals were correctly terminated at the scope end. The scope measuring bandwidth was 200 MHz, and the digital persistence of the traces was set to 5 seconds.

In practice, this means that all the jitter fluctuations of the bench generator and the ADDA16's clock module were displayed during a continuous 5 seconds window. The jitter magnitude would be measured as signal jitter + the PLL jitter. This is the correct and established way to measure jitter.

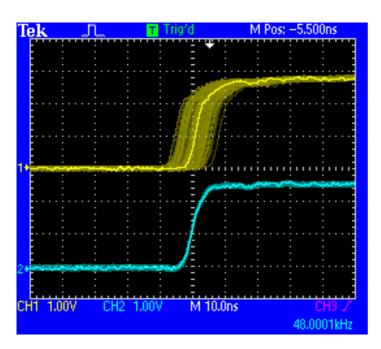

The upper trace shows the jittery clock sent to the input of the clock module and the lower trace shows the regenerated output clock with a nice and clean leading edge. The time scale is 10 nsec per division.

### But let's take a closer look

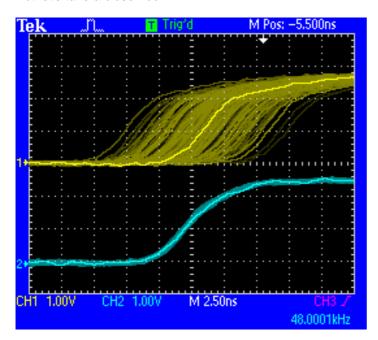

At 2.5 nsec per division, the output jitter begins to become visible. So let's look even closer

Adding 5x gain on the trace that shows the output jitter, reveals the true amount of jitter to be approx. 500 psec PP, which is approx 80 ps RMS.

The measured output jitter is of the same magnitude as when the clock module is running on the internal reference. Using External sync lock or using internal reference doesn't matter. The jitter specs are invariably excellent.